PRODUCT パワーエレクトロニクス

- ホーム >

- パワーエレクトロニクス

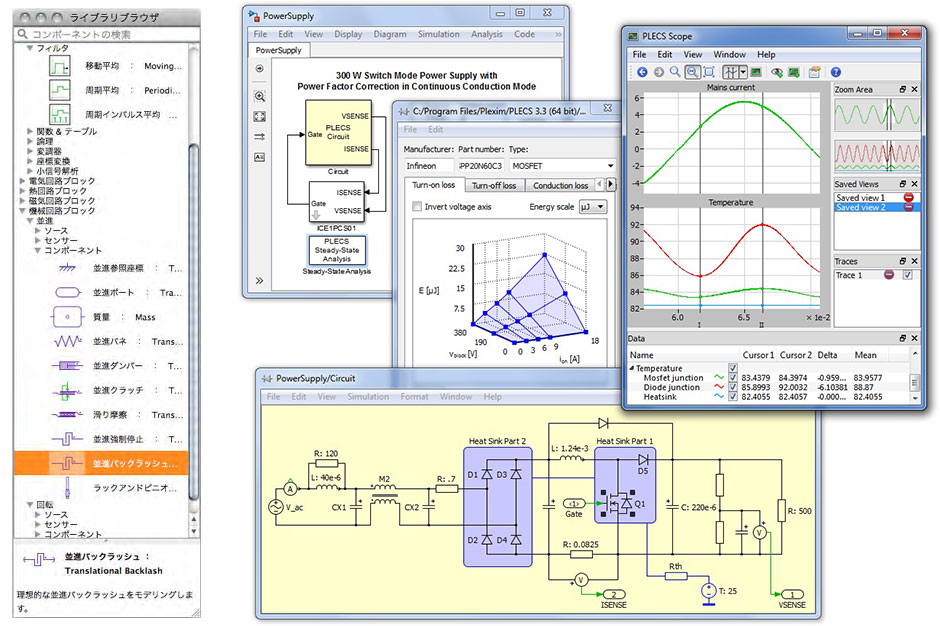

パワーエレクトロニクス向け高速シミュレータ

PLECS®は、制御を伴う、複雑な電気/電力システムを仮想空間上にモデリングし、シミュレーション(仮想実験)を実行するために開発された、「パワエレ・回路/システム・シミュレータ」です。 パワエレシステム開発の上流工程においては、システム全体の応答検証に焦点をあわせ、理想スイッチを用いることで、素早くシミュレーションを実行します。また、下流工程において重要となる、素子の寄生効果等の詳細特性も考慮することが可能です。 PLECSは、非常にシンプルなGUIを採用しており、直感的な操作で、簡単にパワエレシステムを構築します。 また、理想スイッチを用いたスイッチング現象の取扱いによって、高速かつロバストなパワエレ回路シミュレーションを実行することが可能です。 シンプルなチョッパ回路、または複雑な電動機回路といったシミュレーション対象のモデリング難易度に関わらず、必要とする結果を、素早く手に入れることが可能なパワフルなシミュレーションツールです。

RT BOx

RT Boxは、パワエレ用アプリケーションに特化して設計されたリアルタイムシミュレータです。 多数のアナログおよびデジタル入力/出力チャネルとSoC(CPUコア搭載FPGA)により、リアルタイムでハードウェア・イン・ザ・ループ(HIL)および、ラピッド・コントロール・プロトタイピング(RCP)を実行/処理します。 RT Box には仕様条件に合わせ複数のバリエーションが用意されています。

RT Box 製品一覧

RT Box には使用条件に合わせ複数のバリエーションが用意されています。

技術仕様の違いを確認するには以下の仕様比較表 を参照して下さい。

- HILS(Hardware-in-the-Loop Simulations)

- RCP(Rapid Control Prototyping)

- 外部H/W接続用インターフェース

- PLECS RT Boxの仕様

- PLECSシミュレータとの連係

- 技術仕様詳細

- 適用事例 : 系統連系MMCのHILシミュレーション

HILS(Hardware-in-the-Loop Simulations)

通常、制御ハードウェアの入力信号は、電圧/電流センサから出力されるアナログ信号となります。 HILシミュレーションでは、これらの信号が、PLECS RT Boxのアナログ出力チャンネルから出力されます。 速度測定用ホール効果センサー等のデジタル信号は、PLECS RT Boxのデジタル出力チャンネルから出力されます。

パワエレ用途の制御器は、個別のパワー半導体を制御するために多数のPWM信号を生成します。 PWM信号は、PLECS RT Boxのデジタル入力によって、10ns以下の時間分解能で検出可能です。 検出された入力データを適用して、PLECS RT Boxは電力変換器をエミュレートし、数マイクロ秒後、アナログ信号で、その計算結果を出力します。 I/O入出力の短い遅延時間によって、接続された制御ハードウェアは、実際の変換器システムが実装されているように動作します。

RCP(Rapid Control Prototyping)

PLECS RT Boxを2台使用する場合、BTB(Back To Back)の完全システムをテストすることが可能になります。 この場合、1台は電力変換器をエミュレートし、もう1台は制御器となります。

外部H/W接続用インターフェース

外部ハードウェアとの接続用インターフェースとして、ブレークアウトボードとインターフェースカードセットが用意されています

アナログ・ブレークアウト・ボード

各アナログ信号I/O端子に対しBNCソケットを介してアクセスします。

デジタル・ブレークアウト・ボード

各デジタル信号I/O端子に対し端子ブロックとピンヘッダを介してアクセスします。

LaunchPadインターフェース

TI社が販売している「LaunchPad, LaunchPad XL開発キット」とPLECS RT-Boxとの接続を容易にします。

ControlCardインターフェース

TI社が販売している「各ControlCard」とPLECS RT-Boxとの接続を容易にします。

外部H/W接続用インターフェースに関するユーザーマニュアルをご希望の方は下記フォームよりご請求ください。

PLECS RT Boxの仕様

プロセッサ

アナログI/O

アナログ入力は、コモンモードEMI(Electro-Magnetic Interference)を抑制する、差動入力です。 必要な場合は、シングルエンド入力も対応可能です。

デジタルI/O

PLECSシミュレータとの連係

PLECS RT Boxは、PLECS StandaloneとPLECS Coderが実行可能なホストコンピュータと連係して使用します。 PLECS Coderは、PLECS RT Boxのリアルタイムシミュレーションで実行するため、 仮想空間上のPLECSシミュレーションモデルを、Cコードへ自動で変換します。 ホストコンピュータ上のPLECSシミュレーションモデルは、 外部モードを使用して、PLECS RT Boxのリアルタイムシミュレーションと接続可能です。 これにより、PLECS RT Boxのシミュレーション結果を、 ホストコンピュータ上のPLECS Scopeに表示し、 パラメータの設定を、より簡単に変更することが可能になります。

技術仕様詳細

| RT Box CE | RT Box 1 | RT Box 2 | RT Box 3 | ||

|---|---|---|---|---|---|

| プロセッサ | Xilinx Zynq | Z-7030 | Z-7030 | ||

| CPUコア | 2 x 1 GHz | 4 x 1.5 GHz | |||

| アナログ入力 | チャンネル数 | 8 | 16 | 32 | |

| 分解能 | 16ビット(同時サンプリング) | ||||

| 電圧範囲 | -10 … 10V

-5 … 5V |

||||

| 入力方式 | 差動入力 | ||||

| 最速サンプルレート | 2Msps | 5Msps | |||

| 入力インピーダンス | 1MΩ, 24 pF | ||||

| 接続端子 | 37ピンD-subコネクタ(オス) | ||||

| アナログ出力 | チャンネル数 | 16 | 32 | ||

| 分解能 | 16ビット(同時サンプリング) | ||||

| 電圧範囲 | -10 … 10V

0 … 10V -5 … 5V 0 … 5V |

||||

| 最速サンプルレート | 2Msps | 5Msps | |||

| 出力インピーダンス | 0Ω | ||||

| 最大出力電流 | 10mA | ||||

| 接続端子 | 37ピンD-subコネクタ(オス) | ||||

| デジタル入力 | チャンネル数 | 32 | 64 | ||

| ロジック・レベル | 3.3 V [5V tolerant] | ||||

| 接続端子 | 37ピンD-subコネクタ(オス) | ||||

| デジタル出力 | チャンネル数 | 32 | 64 | ||

| ロジック・レベル | 3.3V

5V |

||||

| 接続端子 | 37ピンD-subコネクタ(オス) | ||||

| レゾルバ | 入力/出力数 | -/- | 1/1 | 2/2 | |

| 接続端子 | 9ピンD-subコネクタ(オス) | ||||

| I/O保護 | 短絡 | Permanent | |||

| 過電圧 | -24 … 24V | ||||

| 接続方法 | Gigabit Ethernet | 1 | 2 | ||

| SFP + interconnects 6.25

Gbps per lane |

1 | 4 | 8 | ||

| Industrial Ethernet | – | 2 | |||

| CAN bus | 2 | ||||

| RS 232/422/485 | – | 2 | |||

| USB A 2.0/3.0 | 1/- | -/1 | |||

| ディスプレポート | 1/- | -/1 | |||

| ストレージ | 内臓SSD | – | 480GB | ||

| ファームウェア | SD card | ||||

| 電源(内臓) | 100 … 240 Vac

50 … 60 Hz |

30 VA | 50 VA | 65 VA | 100 VA |

| サイズ | 奥行×幅 | 225 x 165 mm | 310 x 250 mm | ||

| 高さ | 55mm | 100mm | 145mm | ||

適用事例 : 系統連系MMCのHILシミュレーション

適用事例 : 系統連系MMCのHILシミュレーション

PLECS RT Box は最新鋭の汎用リアルタイムシミュレータです。32端子のアナログ入出力チャンネルと64端子のデジタル入出力チャンネルが実装されており、1GHzのデュアルコアCPUが、ハードウェア・イン・ザ・ループ(HIL)/ラピッド・コントロール・プロトタイピング(RCP)のシミュレーションをリアルタイムに実行/処理します。

上図は、4台のRT-Boxを使用した系統連系モジュラーマルチレベルコンバータ(MMC)のリアルタイムシミュレーション環境です。MMCの各相レッグに接続されている10個のハーフブリッジには、それぞれスレーブ制御器H/Wが接続され、個別のRT-Box上でリアルタイムシミュレーションを実行します。4つのRT-Boxの最上部では受動フィルタと系統がモデリングされています。RT-Boxは、背面の高速シリアルリンクを介して相互に接続した状態でシミュレーションデータ情報を通信し、シミュレーションステップを同期します。すべてのRT-Boxがサンプリング時間(時間刻み):3μsで動作しています。

制御ロジックは4つのマイコン(TI社:C2000マイクロコントローラ)に実装されており、 LaunchPadインターフェースボードを介して、各RT-Boxの前面に接続されています。 最上部のマスター制御器H/Wは、SPIバスを介してスレーブ制御器H/Wと通信します。

MAIL FORM24時間受付